#### 促進產學合作先導型研究計畫IV

# 基於微機電系統技術之高產能多電 子束平行寫入微影系統之研發

## Design of MEMS-based Massively Parallel Maskless Electronbeam Lithography Systems

#### 文 · 圖/顏家鈺 (機械工程學系教授)

執行 期限:民國95年8月1日起至民國96年12月31日止

主 持 人:顏家鈺

共同主持人:陳永耀、鍾添東、蔡坤諭、王富正、盧奕璋、李佳翰、許博淵

年來傳統光學微影技術逐漸達到極限,使用 波長193奈米光源可達成電晶體半間距約爲65 奈米。如果再配合以濕浸式微影技術(immersion lithography),此半間距極限可望提升至45 奈米。若無 其他顛覆性的突破,傳統式的微影方式的解析度由於 光波波長的物理基本限制已經達到極限。然而國際間 預測半導體的半間距在5年內會縮小至32奈米。至於 下一代的製程會需要何種「微影技術」,現在科技 界尚未有明確的定論。目前各種可能的次世代微影選 項不外乎使用波長更短的光,甚至直接以物質波來降 低波長的限制,電子東直接寫入是直接以電子爲寫入 的媒介,因此是一種極具潛力的技術。電子東直接寫 入的優勢在於不需要昂貴複雜的光罩(相對於 EUV)、高景深高解析度(相對於光學微影),及 安全的工作距離(相對於 Imprint)。若將大量的電 子束同時運做於晶圓微影製程上,理論上可以符合業 界對產能的需求。本計畫重點在: (一)以 MEMS

製程技術爲核心開發微電子電極陣列作爲高速度之微 電子發射源; (二)設計低像差、製造單純之微電 子透鏡系統; (三)能偵測電子束偏移之感測器; (四)針對多電子束微影系統所需要之規格研製其真 空腔及防震系統。希望藉本計畫的發展一方面能降低 整體微影系統之價格,一方面可以協助協力廠商-台 積電公司建立下一代微影設備的技術,提升台積公司 的競爭力。藉由與台積公司的合作,本計畫希望能成 爲臺灣產學界共同研發半導體微影設備之先例,期能 帶動臺灣半導體設備產業在全球的競爭力。

#### 計畫簡介

逾半世紀以來,單一晶片上的元件密度按摩爾定律 (Moore's Law)[1],以每一年半增加1倍之速度前進,半 導體製程的進步日新月異,以往所謂次微米的技術今 日已減小到90 奈米的製程,而產業界並不以此爲滿 足,仍然不斷的尋求繼續縮小積體電路尺寸的方法。

而在眾多的製程方法中,「電子束微影」目前被認 爲是最具有潛力發展成爲次世代半導體製程設備的技 術。本計畫因此規劃從事「電子束微影系統」的開 發,從自行設計規劃此系統的電子光學系統與腔體來 檢討「電子束微影系統」在實際應用上所遭遇的困 難,並提供相關的改進設計。根據2004年國際半導 體技術藍圖(International Technology Roadmap for Semiconductors, ITRS<sup>[2]</sup>), 目前 193 奈米深紫外光(Deep Ultra Violet, DUV)技術是90奈米量產製程的主流,藉由 微影技術與晶片設計軟體的垂直整合(Lithography Friendly Rules, LFR),外加光學鄰近效應修正法(Optical Proximity Correction, OPC<sup>3</sup>)的應用,193 奈米深紫外光技 術半間距寬度仍可向下縮減,2007年到來的65奈米 23 技術節點將是 193 奈米技術的極限。而浸潤式 193 奈米技術4151達成2009年45奈米技術節點亦已成爲業 界共識,然而,2010年45 奈米以下之微影技術為 何,目前仍無定論。由於傳統透鏡無法有效聚焦極短 波長之紫外光(Extreme Ultra Violet, EUV)與X光,因此光 學微影技術由深紫外光過渡至極紫外光將面臨光學系 統設計的重大變革,輔以光源產生與光罩製作的困 難,極紫外光微影陷入高技術開發難度與高製造成本 的窘境。由於單一組最先進製程光罩製作花費已超過 100 萬美金,而一組光罩設計圖藉由光學鄰近效應計 算得到修正後的圖案,以大量電腦平行運算仍需耗費 數天的時程。因此,面對愈益高漲的晶片製造成本, 業界對於傳統以光罩爲基礎的微影技術發展的經濟效 益以產生極大的懷疑與憂慮[7],無光罩微影技術 (Maskless lithography, ML26)也從此被寄予厚望,有機會 一躍成爲次世代微影技術的主流。

多電子東平行掃瞄技術可憑藉其成本優勢,躍居 32 奈米微影技術之主流。電子束微影術近年已廣泛應 用於先進製程之光罩製作,其理論解析度可達數奈 米,考慮電子與光阻交互作用產生之鄰近效應 (proximity effect),電子束微影術仍可輕易達成20奈米 的線寬要求;此外,由於電子束的聚焦角度甚小,因

此電子束微影術具有接近微米等級的焦深(depth of focus, DOF), 為其他光學微影術所無法比擬的[8]-[11]。 經過數十年對於傳統的電子束微影技術與電子顯微鏡 的研究,半導體業界無論在電子槍、電子透鏡、對應 之光阻以及鄰近效應等性質已有相當的瞭解,挾著高 解析度與長焦深的優勢,利用多道電子東平行寫入, 可大幅改善單一電子束直接寫入(electron beam direct write, EBDW)產能不足的窘境,進而幾近工業應用之產能標 準(約每小時60片晶圓);由於多電子東平行掃瞄 無光罩微影術極具未來工業應用潛力,因此,以多電 子東平行掃瞄爲基礎之無光罩微影技術開發近年已成 爲次世代微景/技術(next generation lithography, NGL)研究 的顯學。

本計畫以高產能電子束微影系統爲最終目標,嘗試 研發設計使用微機電技術製造所需之陣列電子發射 源、陣列電子透鏡(成像及遮黑板)系統及電子東漂 移感測陣列。限於篇幅以下報告其中電子發射源與散 射電子感應器的製作成果。

#### 執行成果

#### (一) 電子束探頭設計與製作

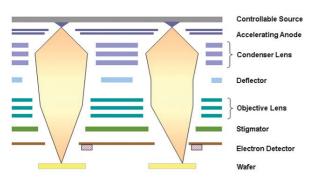

本計畫目的爲以微機電的技術開發陣列式平行發射 電子束的電子束發射源。整體的設計概念如圖 1 所 示。

電子束採用冷場發射的方式產生。電子束發射有熱 發射、熱場發射與冷場發射等方式。由於本計畫所執 行的電子束是用來作半導體製程設計圖案寫入,因此 強調的是耐用性與機構單純,冷場發射的電極設計最 符合本計畫的需求。冷場發射在已知電子束發射源 中,被認爲有壽命時間長、能量分布範圍小、聚焦點 直徑小等優點;至於發射源之材料的部分選用微機電 製程常用的矽半導體,可整合發展純熟的微機電技術 來製作電子束發射源。冷場發射的電極需要非常尖銳 的電極方便電子發射,同時需要在鄰近電極探頭的附 近製作電場電極,以降低電子束發射的能場。

圖 1:多探頭電子束微影設備示意圖。

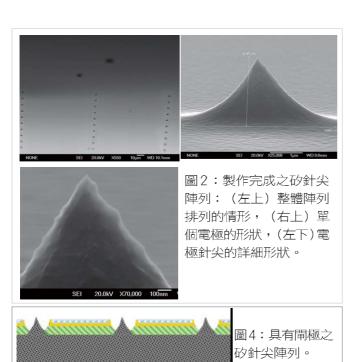

本計畫的電極陣列,是在矽基板上以熱氧化成 長二氧化矽,作爲蝕刻矽時的擋層材料,以光微 影技術製作出電極陣列,再以傳統 CMOS 製程將 矽基板上的材料成形、削尖形成矽針尖陣列。圖 2 所示是本計畫所製作的電極陣列,本計畫的製 程可以將針尖削尖到十幾奈米的程度。

做好矽針尖陣列後,另外以微機電製程製作能 夠懸浮在矽針尖上而不會導致短路的導電層(陽 極板),如圖3所示。將矽針尖陣列作爲陰極與 陽極板疊合後,未來置入真空度在10-9 torr 的真空 環境下,將陰極接地、陽極給予正電壓,則會在

玻璃

圖 3:陽極板金屬層的設計圖形與陽極陰極疊合情形示意圖。

每個矽針尖頂端處產生強大的電場,將電子從矽 固體內以場發射的原理釋放出來,產生出陣列式 平行的電子束,量測電子束的性能。

目前本計畫正在進行以微機電製程在矽針尖頂端周 圍製作一層金屬層,如圖4所示。

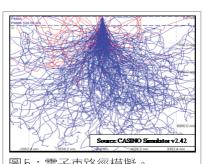

爲切實了解電子東射入基材之後所產生的寫入效 應,本計畫並進行電子東寫入點散溢情形的模擬。圖 5 與圖 6 所顯示的是電子東在聚焦後射入基材的情 形。由於電子之間相互作用與電子行進中撞擊基材原 子的效應,電子東射入基材後有強烈的發散現象,如 果要寫出精密的曝光圖形,則電子束的能量需要非常 精密的控制。圖6是聚焦點發散能量分布的情形,藉 此圖可以協助吾人建立電子束能量的規劃原則。

#### (二) 電子東射線定位回饋控制

在多電子東微影技術中,電子東偏移成為一個越

圖5:電子束路徑模擬。

Normalized energy radial distance (nm)

圖6:電子聚焦點發散函數分布。

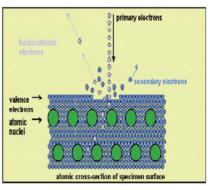

來越需要被重視的 議題。造成電子東 偏移的原因有很 多,如試片表面的 電荷殘餘,腔體中 溫度的不穩定,污 染…等。這些偏移 會影響微影技術中 的精準度和電子束 的對焦,而且這些 誤差會隨著操作時 間增長而增加。當 一電子東打在試片 上時,會產生各種 類型訊號(圖7),

其中一種就是由電子產生,最主要的電子訊號又分 成兩類,分別叫做"二次電子"與"背向散射電子", 這兩種電子常常被用來在電子顯微鏡中呈現影像, 顯示試片的表面及構造。當電子束打在試片上時, 電子會與試片上的原子核產生交互反應,帶負電的 電子會被帶正電的原子核吸引,若是電子沒有被原 子核"捕捉",電子行進的方向則會在損失很少能 量和速度的狀況下,產生大角度的變化,這些發生 角度變化的電子,被稱爲"背向散射電子"。在一 個電子顯微鏡中,背向散射電子感測器經常被放置 在試片的正上方,藉以捕捉這些回彈的電子。因爲 背向散射電子移動的速度快,能量高(圖8)[12],相 較於二次電子,他們比較不容易被外在的電場影響 而改變方向,我們將針對背向散射電子彈射的分布 進行研究與模擬,並期望分析二次電子分布與入射 電子束偏移的關係,進而發展出一套能及時監控電 子束位置的感測器系統。

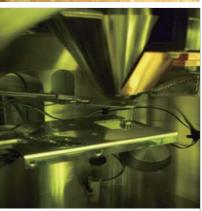

爲了探究電子束位置,與背向電子散射方向的關 係,我們利用蒙地卡羅法(Monte Carlo)建立電子東與 試片產生交互作用時,背向散射電子的行進軌跡, 用以推導電子東原始位置,並找出背向散射電子感 測器的安裝位置和工作距離,以得到最佳的電子收 集率。同時已在掃描式電子顯微鏡上(Scanning Electron Microscopy, 圖 9), 架設四像限光電二極體感測器,量 測其感測到之背向散射電子訊號,藉由電子束之定 點掃描訊號,建立標準校正訊號,以期許達成電子 束位置的漂移校正, 並增加電子東直寫的穩定性及 精準度。

#### 目前進度

本計畫第一年已經有相當豐富的成果,本計畫與台 積電公司密切聯繫與溝通,台積電公司願意以更多經 費來支持本計畫,所以依本校研發會所設定的要求, 提早在第二年度轉型,以台積電的經費向國科會爭取 先導型計畫,目前正積極籌組團隊和撰寫計畫書中。

### 羹(本專欄策畫/研究發展 處)

#### 參考資料:

- [1]Gordon Moore, "Cramming More Components Onto Integrated Circuits," Electronics Magazine, 1965

- [2]International Technology Roadmap for Semiconductors, 2004 Update, Available at http:// /public.itrs.net/

- [3] Moore's Law, at Intel Website at http://www.intel.com/technology/silicon/mooreslaw/

- [4]F. Schellenberg, "Resolution enhancement technology: The past, the present, and extensions for the future," SPIE 5377, pp. 1-20, 2004.

- [5]Burn J. Lin, "Immersion lithography and its impact on semiconductor manufacturing", accepted for publication in J. Microlith., Microfab., Microsyst., vol. 3, 2004.

- [6] Burn J. Lin, "New insight for maskless lithography," JM3, 4 (2),2005

- [7] Rieger, Michael L., Stirniman, John P., "Customizing proximity correction for processspecific objectives," Proc. SPIE Vol. 2726, p. 651-659, 1996

- [8] Rajesh Menon, Amil Patel, Dario Gilt, and Henry I, "Maskless Lithography," Materials Today, www.

materialstoday.com, p.26-33, Feb. 2005

- [9] James R. Sheats (Editor), Bruce W. Smith (Editor), "Microlithography: Science and Technology," Marcel Dekker, ISBN: 0824799534, 1998

- [10]Aaron Hand, "Infrastructure Steps Closer to EUV Lithography," Semiconductor International, 2005/09/01

- [11]C. E. Hall, "Introduction to Electron Microscopy," second edition, McGraw-Hill, 1953

- [12] Hans C Pfeiffer, presentation for Sematech Litho Forum, 2004

由上而下:

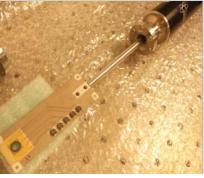

圖7:電子束與試片的交互反應。 圖8:四像限光電二極體感測器。

圖 9: 感測器架設於電子顯微鏡內 部。